#jest

|

|

-

@FoxMurder: Zobacz, swoją drogą Owen ma tyle kasiorki, że operacji plastycznych mógłby zrobić ze pincet. A mimo to krzywego nochala nie rusza- jego dewiza . Bez niego nie byłby już taki sam.

-

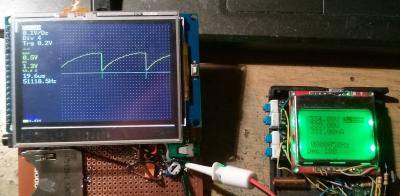

No więc ten wewn ADC w Xmega da się cisnąć nawet na ok 13-14MSPS przy użyciu DMA i przetaktowaniu na aż 48Mhz core ale oczywiście spada wtedy rozdzielczość do 6-7bit, ale to nadal zupełnie przydatne i dobrze wygląda. Ale zależy od amplitudy sygnału, to co tu widać nie przekracza 1V.

Niestety zewn ADC osiągał słabą prędkość ok 8-9 MSPS co jest dość dziwne. Przecież wykorzystywał ten sam sposób z DMA

Może jeszcze jakby wykorzystać drugi wewn adc i je trigerować na zmianę i przepleść wyniki to by osiągał 2x więcej sampli/s. Trzeba będzie pokombinować.

#xmega #avr #elektronika Podgląd | Rozmiar pliku: 173 KB

Podgląd | Rozmiar pliku: 173 KB+: fanzonun

-

BYłem ostatnio w kawiarni i widziałem jak przdemną stoi 2 mężczyzn w srednim wieku a przed nimi jakas biedna staruszka. Ogolnie na 1 rzut oka bylo widac ze jest bezdomna albo bardzo niezamożna. Błagała na kolanach sprzedawace żeby jej dał zupe bo bylo mrozno na dworze, jakies -12*C, ale sprzedawca jej tlumaczył. Glupia babo to kawiarnia tutaj nie ma zupy. 2 mezczyzn kazało jej wypierdalac i byli bardzo zazenowani bo przeciez wiadomo, ze nie obsluguje sie przeciez(!) takiej hołoty jak ta baba. Sprzedawca oczywiście przyznal im racje bo istotnie ją mieli. Stalo sie tak, ze w koncu sprzedawca, ci mezczyzni i ja zaczelismy ja wyzywac i kazac wypierdalac. Dolaczyli sie nawet postronni klienci kawiarni bo jak widac nie pasowalo im ze jakis swołocz powoduje tak ogromne zamieszanie w lokalu.. Cale szczescie babsko polazło, a ja moglem w spokoju zamówić i zjesc pomidorówkę.

#takbylo #takaprawda #wujekbenjestdumny #lashatosmiec

masz @lasha bo chyba cie #smieciu ominelo

j@%any archiwalny post

-

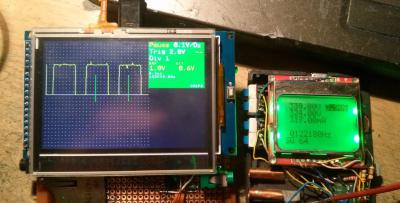

Miałem za duże mniemanie o tym parującym klocu którym jest Xmega.

nie oznacza to jednak że jest bezużyteczna.

przykładowo na wewn ADC da się wyciągnąć ok 8-9MSPS w 8bitowej rozdzielczości, nie jest to wcale zły wynik na adc w avr i basicu.

Problem jest w tym że DMA w połączeniu z szyną danych poprzez którą się łączę z ADC powinna chyba wycisnąć więcej niż pożal się boże 9MSPS. Bo tyle chyba udało mi się wydusić, i to przy kręceniu wora na 50Mhz a fabrycznie powinno być 32Mhz (nie dzwońcie na policję). lipa mocno. Może jest ekspert na sali od DMA? Może bez znaczenia dla języka wie czy da się wykombinować większą prędkość toczenia danych bo chyba tu jest problem w prędkości owego DMA.

Bo to było tak, ADC udaje ram bo przy każdym cyklu zegara który bierzemy z pinu ramu read enable otrzymujemy próbkę. Tak jakbyśmy wyciągali dane z array z zewn RAMu. array>array. Proste w sumie. Ale ponoć DMA miałobyć takie kurła szybkie że niby 2x zegar, a ten marnuje masę cykli na przetoczenie. A ram ustawiony na max, bez waitstait. Co prawda to blisko prędkości granicznej ADC1173 czyli 15MSPS ale szkoda nie wykorzystać tych 5-6MSPS. #xmega #avr #elektronika Podgląd | Rozmiar pliku: 163 KB

Podgląd | Rozmiar pliku: 163 KB+: fanzonun

-

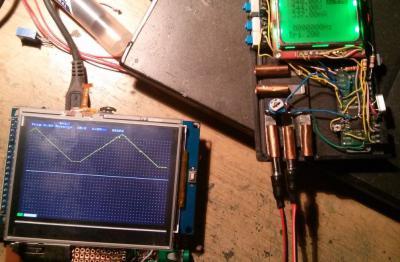

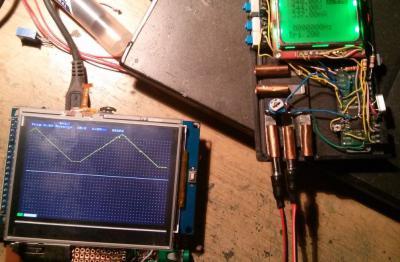

Uruchomiłem zewn ADC 8bitowy na szynie równoległej. Normalnie odpowiednio sterowany może wycisnąć jakieś 15MSPS, ale niestety nie umiem programować w takie układy. Miałem nadzieję że będzie tak szybki jak wewn ADC xmega ~2MSPS na maksymalnie uproszczonym kodzie ale niestety tak nie jest. Wyciska jakieś 0,8MSPS. Co jest bezwartościowe jak moje życie.

Ale podłączyłem go do portu sterowania zewn ramem więc może da się więcej z niego wycisnąć.

Tym bardziej że EBI bo tak się nazywa ta szyna zewnętrzna może ganiać 2x szybciej niż Core xmegi czyli jak ganiasz kloc na 32Mhz to EBI na 64Mhz.

Daj bug żeby z tego coś wyszło bo się potnę mokrym herbatnikiem.

#xmega #avr #elektronika Podgląd | Rozmiar pliku: 137 KB

Podgląd | Rozmiar pliku: 137 KB -

@horteksic: dzięks. Niestety nie wiem jak to dopracować operowanie na zzewn szynie za pomocą DMA bo robi bałagan już po 2 próbce, 1 jest ok potem się coś paprze.

Najlepsze że to bascom a guwnospecjaliści twierdzą że basiciem można sobie co najwyżej leda zaświecić.

-

Uruchomiłem zewn ADC 8bitowy na szynie równoległej. Normalnie odpowiednio sterowany może wycisnąć jakieś 15MSPS, ale niestety nie umiem programować w takie układy. Miałem nadzieję że będzie tak szybki jak wewn ADC xmega ~2MSPS na maksymalnie uproszczonym kodzie ale niestety tak nie jest. Wyciska jakieś 0,8MSPS. Co jest bezwartościowe jak moje życie.

Ale podłączyłem go do portu sterowania zewn ramem więc może da się więcej z niego wycisnąć.

Tym bardziej że EBI bo tak się nazywa ta szyna zewnętrzna może ganiać 2x szybciej niż Core xmegi czyli jak ganiasz kloc na 32Mhz to EBI na 64Mhz.

Daj bug żeby z tego coś wyszło bo się potnę mokrym herbatnikiem.

#xmega #avr #elektronika Podgląd | Rozmiar pliku: 137 KB

Podgląd | Rozmiar pliku: 137 KB -

@horteksic: dzięks. Niestety nie wiem jak to dopracować operowanie na zzewn szynie za pomocą DMA bo robi bałagan już po 2 próbce, 1 jest ok potem się coś paprze.

Najlepsze że to bascom a guwnospecjaliści twierdzą że basiciem można sobie co najwyżej leda zaświecić.

-

@kvlr: wgl zastanów się jak reprezentujesz ten szacowny portal w oczach kulturalnych użytkowników internetu

© Copyright 2005-2026 Milanos.pl Wszystkie prawa zastrzeżone. Korzystanie z serwisu oznacza akceptację Regulaminu

Strona główna

Strona główna

FoxMurder

ponad 8 lat temu

Coś jest nie tak z sygnałem końca linii, chodzi o to że w każdej kolejnej linii jest to samo co w pierwszej.

Prawdopodobnie coś nie tak nie tylko z umiejscowieniem kolejności zakładania sygnału HSYNC, ale także chyba też z czasem. To samo dotyczy chyba VSYNC. Na oscyloskopie widać że te sygnały są. Nie wiem jak to naprawić bo brak dokumentacji do tego konkretnego wyświetlacza, nawet nie wiem właściwie czy dobrze próbuję tym sterować. #elektronika #xmega

Są sygnały standardowe chyba, pinologia pasuje jak w wielu innych, jest sygnał FLM, CP1 CP2 lub też można je uznać za Latch Clock no i 4bitowa szyna danych. 1 sygnał zegara na każde 4 bity.

+: Lasha, kvlr, fanzonun

horteksic

ponad 8 lat temu

@FoxMurder: Xmega128a1u, bujana na właściwie dowolnej prędkości od 2Mhz do 48 nawet.

Lcd na wypasie bo 320x480, wszystko pisane w bascom i asm ale uwaga ja nie napisałem całego sterownika do lcd.

Ale napiszę następny pseudo skopometr. Czyli multimetr i niby oscyloskop, niby bo oscyloskop będzie powolny, ale zawsze coś. Zawsze mnie wkurwiało że nawet w drogim mierniku mam do pomiaru zawsze jedną rzecz jednocześnie. Tu będzie naraz 2x napiecie, prąd do 1A (chyba) i ów oscyloskop. Będę próbował zawiesić na szynie zewn 8bit zewn ADC, może uda się wydusić z 4MSPS. A kto wie może i więcej.

Kiedyś wrzucałem poprzedni w obudowie gameboy z nieco mniejszym LCD.

Widać ładowarkę baterii, a drugie USB do programowania przez PDI. To nieoficjalne złącze bo po prostu w xmega PDI to także 2 kabelki. Ale mogę mieć problemy by upchnąć tu jeszcze jakieś przyciski, multiplekser, i garść nie takich małych precyzyjnych potencjometrów. Do tego gniazdo na sondę i ch#% wie co jeszcze.

+: Lasha

kvlr

ponad 8 lat temu

@FoxMurder: masz racje

-: horteksic